# **Microprocessor Reset IC**

### **Features**

- Precision Monitoring Voltage of +2.2V and +3.7V

- **■** Fully Specified Over Temperature

- Available in Three Output Configurations

Push-Pull RESET Output (G656L)

Push-Pull RESET Output (G656H)

Open-Drain RESET Output (G657L)

- Reset Deassert Time Smaller than 100µs when V<sub>CC</sub> Higher than Monitor Voltages (CD Pin Floating)

- Externally Programmable Time Delay Generator

- 27µA Supply Current at V<sub>CC</sub>=3.3V

- Guaranteed Reset Valid to V<sub>CC</sub> = 0.8V

- TSOT-23-5 Packages

- 2% Threshold Accuracy

### **Applications**

- **■** Computers

- Controllers

- Intelligent Instruments

- Critical µP and µC Power Monitoring

- Portable / Battery-Powered Equipment

- Automotive

### **General Description**

The G656/G657 are microprocessor ( $\mu P$ ) supervisory circuits used to monitor the power supplies in  $\mu P$  and digital systems. They provide excellent circuit reliability and low cost.

These circuits perform a single function: they assert a reset signal whenever the  $V_{\text{CC}}$  supply voltage declines below a preset threshold, with hysteresis keeping it asserted for time delay determined by externally programmable time delay generator after  $V_{\text{CC}}$  has risen above the reset threshold.

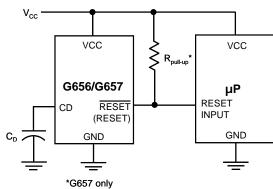

The G657L has an open-drain output stage, while the G656 have push-pull outputs. The G657L's open-drain  $\overline{\text{RESET}}$  output requires a pull-up resistor that can be connected to a voltage higher than  $V_{\text{CC}}.$  The G656L has an active-low  $\overline{\text{RESET}}$  output, while the G656H has an active-high RESET output. The outputs are guaranteed to be in the correct logic state for  $V_{\text{CC}}$  down to 0.8V.

The G656/G657 are available in 5-pin TSOT-23-5 package.

### **Pin Configuration**

# G656/G657 RESET 1 0 5 CD VCC 2 GND 3 4 NC TSOT-23-5 ()is for G656H

## **Typical Application Circuit**

ICC may increased at high T<sub>A</sub>, Therefore, can not connect Resistors to VCC to prevent Icc abnormal behavior at high T<sub>A</sub>.